- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Lapisan Epitaxial: Landasan Perangkat Semikonduktor Tingkat Lanjut

Gambar 1: Mengilustrasikan korelasi antara konsentrasi doping, ketebalan lapisan, dan tegangan tembus untuk perangkat unipolar.

Persiapan lapisan epitaksi SiC terutama mencakup teknik seperti Pertumbuhan Evaporasi, Epitaksi Fase Cair (LPE), Epitaksi Berkas Molekuler (MBE), dan Deposisi Uap Kimia (CVD), dengan CVD menjadi metode utama untuk produksi massal di pabrik.

Tabel 1: Memberikan gambaran perbandingan metode preparasi lapisan epitaksial utama.

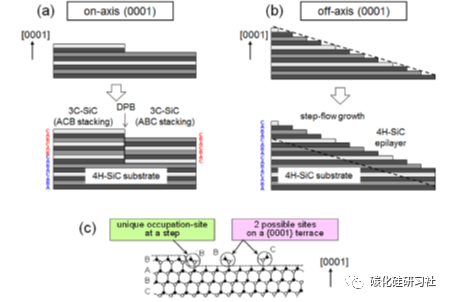

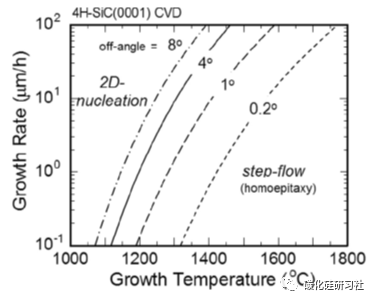

Pendekatan inovatif melibatkan pertumbuhan pada substrat di luar sumbu pada sudut kemiringan tertentu, seperti yang digambarkan pada Gambar 2(b). Metode ini secara signifikan meningkatkan kepadatan langkah sekaligus mengurangi ukuran langkah, memfasilitasi nukleasi terutama di lokasi penggabungan langkah dan dengan demikian, memungkinkan lapisan epitaksial mereplikasi urutan penumpukan substrat dengan sempurna, menghilangkan koeksistensi politipe.

Gambar 2: Mendemonstrasikan proses fisik epitaksi terkontrol langkah dalam 4H-SiC.

Gambar 3: Menunjukkan kondisi kritis untuk pertumbuhan CVD dalam epitaksi terkontrol bertahap untuk 4H-SiC.

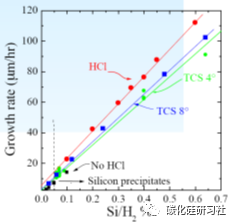

Gambar 4: Membandingkan tingkat pertumbuhan pada sumber silikon yang berbeda untuk epitaksi 4H-SiC.

Dalam bidang aplikasi tegangan rendah dan menengah (misalnya, perangkat 1200V), teknologi epitaksi SiC telah mencapai tahap matang, menawarkan keseragaman yang relatif unggul dalam ketebalan, konsentrasi doping, dan distribusi cacat, cukup memenuhi persyaratan untuk SBD tegangan rendah dan menengah. , MOS, perangkat JBS, dan lainnya.

Namun, domain tegangan tinggi masih menghadirkan tantangan yang signifikan. Misalnya, perangkat berkekuatan 10.000V memerlukan lapisan epitaksial setebal sekitar 100μm, namun lapisan ini menunjukkan ketebalan dan keseragaman doping yang jauh lebih buruk dibandingkan dengan lapisan bertegangan rendah, belum lagi dampak buruk dari cacat segitiga pada kinerja perangkat secara keseluruhan. Aplikasi tegangan tinggi, yang cenderung menyukai perangkat bipolar, juga memberikan tuntutan ketat pada masa pakai pembawa minoritas, sehingga memerlukan optimasi proses untuk meningkatkan parameter ini.

Saat ini, pasar didominasi oleh wafer epitaksi SiC berukuran 4 inci dan 6 inci, dengan peningkatan bertahap dalam proporsi wafer epitaksi SiC berdiameter besar. Ukuran wafer epitaksi SiC pada dasarnya ditentukan oleh dimensi substrat SiC. Dengan substrat SiC 6 inci yang kini tersedia secara komersial, transisi dari epitaksi SiC 4 inci ke 6 inci terus berlangsung.

Seiring kemajuan teknologi fabrikasi substrat SiC dan peningkatan kapasitas produksi, biaya substrat SiC semakin menurun. Mengingat bahwa substrat menyumbang lebih dari 50% biaya wafer epitaksi, penurunan harga substrat diperkirakan akan menurunkan biaya epitaksi SiC, sehingga menjanjikan masa depan yang lebih cerah bagi industri ini.**